Impact of via density on the mechanical integrity of advanced Back-End-Of-Line during packaging

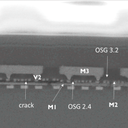

With the introduction of electrically good, but mechanically weak low-k dielectrics the mechanical strength of the BEOL is reduced. This is especially critical during packaging, where there is an increased risk of BEOL failures, due to the high induced stresses. Tasks: The goal is to determine the influence of BEOL metal via density on the packaging yield and crack path in the BEOL. Action: Influence of via density on mechanical integrity of Back-End-Of-Line (BEOL) under Chip Package Interaction (CPI) loading is evaluated utilizing a dedicated package test chip with 4 metal layer BEOL combined in 18 different via density configurations. The assessment is done with pre and post packaging comparison of dedicated CPI test structures. Results: Data indicates a correlation between the BEOL via density and failure rate, showing a concentration of failures at the edges of the chip design space, where at least one BEOL layer has minimum via density. It is also shown that low via density increases the probability of crack propagating in multiple layers of the BEOL stack.The failures are visualized by utilizing SEM.